# Bridge Chip Composing a PCIe Switch over Ethernet to Make a Seamless Disaggregated Computer in Data-Center Scale Takashi Yoshikawa<sup>1</sup>, Jun Suzuki<sup>1</sup>, Yoichi Hidaka<sup>2</sup>, Junichi Higuchi<sup>2</sup>, and Shinji Abe<sup>3 1</sup>Green Platform Res. Labs, <sup>2</sup>System Device Division, <sup>3</sup>IT Platform Division, NEC

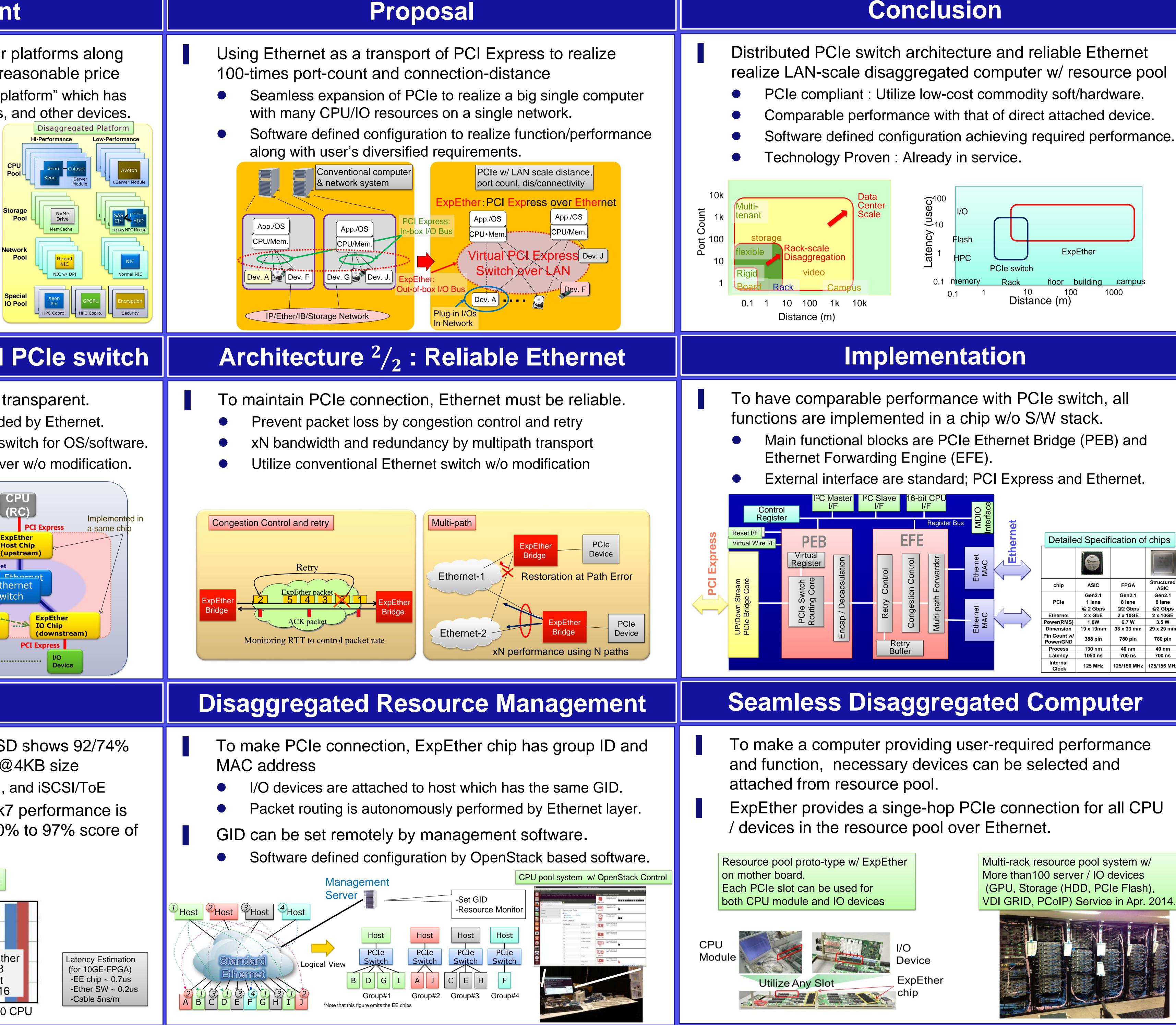

## **Problem Statement**

- Simple protocol, vast hard/soft assets.

- PCIe doesn't reach DC-scale.

- Connection distance and port count are limited to in-box scale.

- Coupling of host and I/O devices are too tight to disaggregate them into shared resource pool.

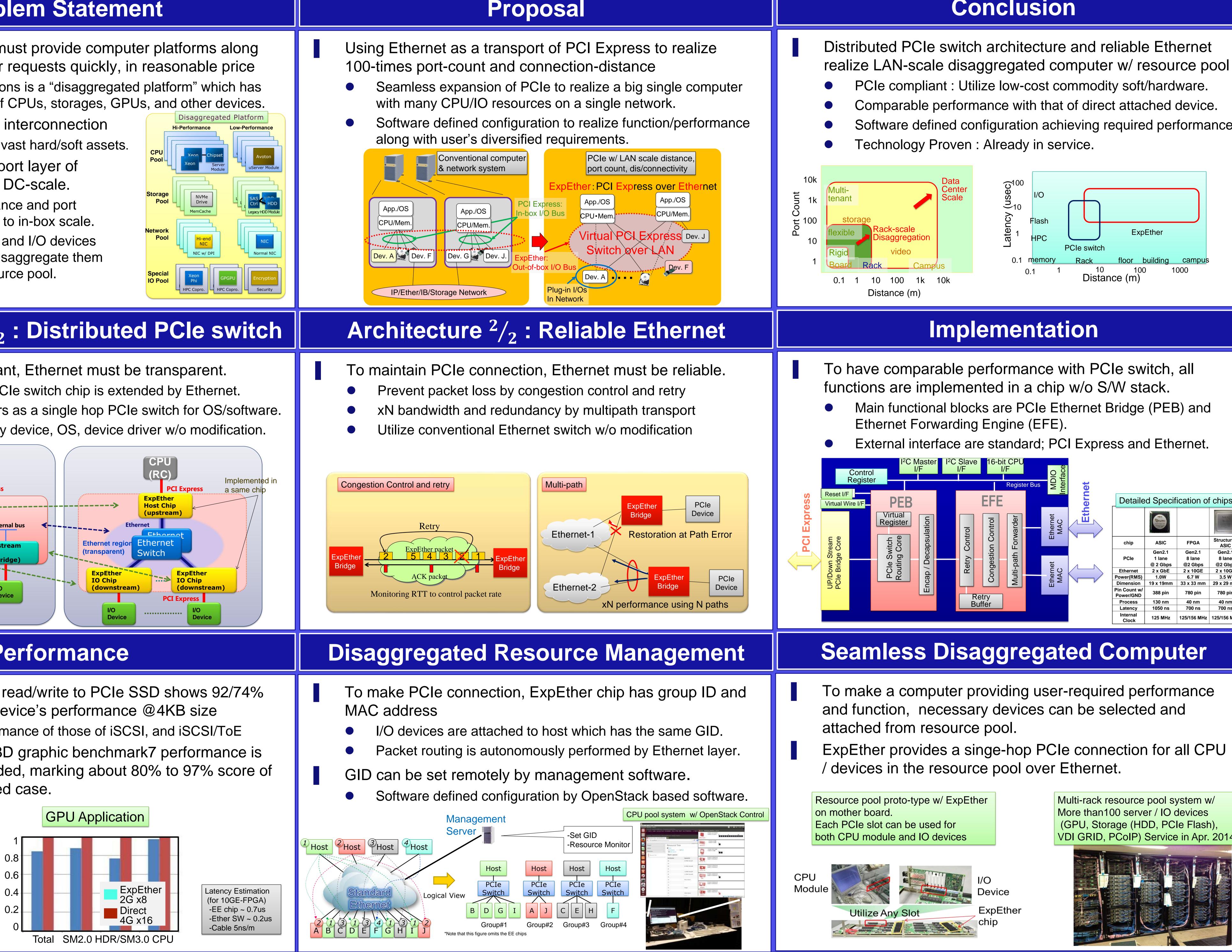

| ave          | 16-                |   | CPU<br>F             |        | MDIO<br>Interface |          |                                 |                                           |                             |                             |

|--------------|--------------------|---|----------------------|--------|-------------------|----------|---------------------------------|-------------------------------------------|-----------------------------|-----------------------------|

| Register Bus |                    |   |                      | er Bus | MD<br>Inter       | let      |                                 |                                           |                             |                             |

| EFE          |                    |   |                      |        |                   | Ethernet | Detailed Specification of chips |                                           |                             |                             |

|              | ontrol             |   | Multi-path Forwarder |        | Ethernet<br>MAC   |          |                                 | NEC<br>Celeviter<br>Harrister<br>Minister |                             | NUCL<br>Marine<br>Transfer  |

|              | Ŭ                  |   |                      |        | ш                 |          | chip                            | ASIC                                      | FPGA                        | Structured<br>ASIC          |

|              | Congestion Control | - |                      |        | Ethernet<br>MAC   |          | PCle                            | Gen2.1<br>1 Iane<br>@ 2 Gbps              | Gen2.1<br>8 Iane<br>@2 Gbps | Gen2.1<br>8 Iane<br>@2 Gbps |

| ř            | È                  |   | ÷=                   |        | ΞO                |          | Ethernet                        | 2 x GbE                                   | 2 x 10GE                    | 2 x 10GE                    |

|              | 8                  |   |                      |        | MAC               |          | Power(RMS)                      | 1.0W                                      | 6.7 W                       | 3.5 W                       |

|              |                    |   | Σ                    |        |                   |          | Dimension                       | 19 x 19mm                                 | 33 x 33 mm                  | 29 x 29 mm                  |

| Retry        |                    |   |                      |        |                   |          | Pin Count w/<br>Power/GND       | 388 pin                                   | 780 pin                     | 780 pin                     |

| Buffer       |                    |   |                      |        |                   |          | Process                         | 130 nm                                    | 40 nm                       | 40 nm                       |

|              |                    |   |                      |        |                   |          | Latency                         | 1050 ns                                   | 700 ns                      | 700 ns                      |

|              |                    |   |                      |        |                   |          | Internal<br>Clock               | 125 MHz                                   | 125/156 MHz                 | 125/156 MHz                 |

VDI GRID, PCoIP) Service in Apr. 2014.